Część sprzętowa modelu

Założenia projektowe

Sprzętowa realizacja modelu polegała na zaprojektowaniu i zbudowaniu urządzenia mikroprocesorowego wyposażonego w układy przetworników A/C i C/A zdolnego do komunikacji z programowa częścią modelu. Środowisko LabView umożliwia prostą obsługę portu szeregowego, co było głównym kryterium wyboru sposobu komunikacji pomiędzy obydwoma częściami modelu. Główne wymagania odnośnie do funkcjonalności sprzętowej części modelu to:

Komunikacja ze środowiskiem LabView za pomocą asynchronicznej transmisji szeregowej opartej na standardzie RS – 232.

Zespół ośmiobitowych przetworników A/C i C/A

Jednostka sterująca oparta na mikrokontrolerze z rodziny ’51

Układ zasilający.

Jako jednostka sterująca użyty został ośmiobitowy mikrokontroler AT89S51 zawierający 4kB pamięci FLASH, układ sterownika transmisji szeregowej oraz interfejs ISP (ang. In System Programable) umożliwiający programowanie za pomocą portu Centronics bez konieczności wyjmowania mikrokontrolera z podstawki.

Port szeregowy umieszczony w strukturze mikrokontrolera działa poziomach logicznych TTL, więc konieczne było zastosowanie dwukierunkowego konwertera poziomów logicznych do standardu RS – 232. Do tego celu został wykorzystany układ MAX 232.

Jako przetwornik C/A zastosowano układ TLC 7226 , natomiast jako przetwornik A/C dwa układy TLC 0820A. Układy te mają rozdzielczość 8 – bitów co pozwoliło na łatwe połączenie z jednostka sterującą. Szczegółowe dane katalogowe tych układów zamieszczone są w dodatku C zamieszczonym na końcu pracy.

Schemat blokowy

Poniżej przedstawiony jest blokowy schemat sprzętowej części modelu, zawierający opisane w poprzednim podrozdziale układy oraz sposób ich wzajemnego połączenia.

Rysunek 3.7. Schemat blokowy części sprzętowej modelu.

Przedstawiony na powyższym schemacie układ posiada:

Cztery wyjścia analogowe AO0...AO3,

Dwa wejścia analogowe AI0, AI1,

Ośmiobitowy dwukierunkowy port cyfrowy,

Linie RxD i TxD do transmisji szeregowej,

Jednostkę sterującą,

Blok przetworników C/A,

Blok przetworników A/C,

Konwerter poziomów logicznych TTL – RS 232,

Blok zasilania.

Schemat ideowy i zasada działania

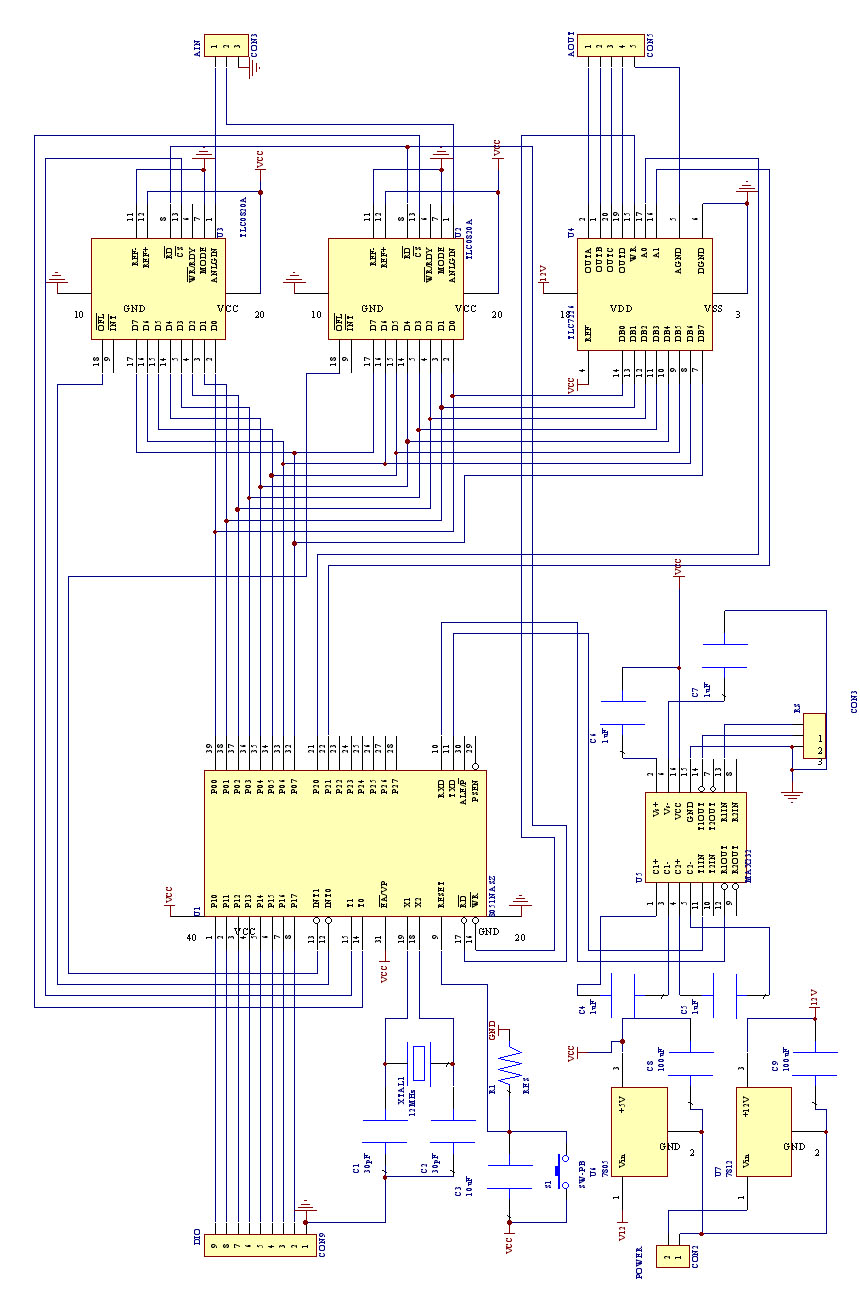

Sterowany model został zaimplementowany programowo w środowisku LabView, natomiast sterownik PLC jest autonomicznym urządzeniem, dlatego należało umożliwić wzajemną komunikacje pomiędzy nimi. Do tego celu została zaprojektowana układowa część modelu współpracująca ze środowiskiem LabView poprzez port szeregowy (RS 232). Schemat ideowy urządzenia przedstawiony jest na rysunku 3.8.

Część sprzętowa modelu zbudowana jest w oparciu o jednostkę sterującą AT 89S51. Mikrokontroler ten jest taktowany wewnętrznym układem zegarowy o częstotliwości 11.059 MHz z dołączonym zewnętrznym rezonatorem kwarcowym. Taka częstotliwość taktowania umożliwia łatwą konfiguracje licznika sterującego portem szeregowym. Cykl rozkazowy mikrokontrolera przy takiej częstotliwości taktowania trwa około 1 ms, co zapewnia szybkie przetwarzanie danych i nie wprowadza opóźnień w działaniu programowej części modelu.

Port szeregowy mikrokontrolera pracuje w trybie 8 – bitowej asynchronicznej transmisji szeregowej o prędkości 1200 bod. Prędkość ta jest wystarczająca do akwizycji danych procesów cieplnych i powoduje jednocześnie minimalizacji błędów transmisji.

Poziomy logiczne napięć na których pracuje port szeregowy mikrokontrolera AT 89S51 są w standardzie TTL, więc do konwersji poziomów logicznych pomiędzy standardem TTL a RS 232 użyty został układ MAX 232 wraz z elementami zewnętrznymi, w typowej aplikacji zalecanej przez producenta.

Dwukierunkowy port P0 mikrokontrolera został wykorzystany jako wspólna 8 – bitowa magistrala danych dla wszystkich układów przetwornikowych. Dwie linie portu P2 wykorzystywane są jako linie adresujące przetwornik C/A. Linie portu P3 służą do uaktywniania przetworników. Cały port P1 dostępny jest na zewnątrz urządzenia jako uniwersalny 8 – bitowy dwukierunkowy port cyfrowy.

Do jego zewnętrznej przestrzeni adresowej dołączone są dwa przetworniki A/C TLC0820

oraz jeden poczwórny przetwornik C/A TLC7226.

Układ TLC 0820 jest pojedynczym 8- bitowym przetwornikiem analogowo – cyfrowym o czasie przetwarzania mniejszym niż 2,5μs. Widok obudowy układu wraz z opisem końcówek sygnałowych przedstawiony jest na rysunku 3.9.

Rysunek 3.8. Schemat ideowy części układowej modelu.

Rysunek 3.9. Widok obudowy układu TLC 0820 wraz z opisem końcówek sygnałowych.

Przetwornik wymaga doprowadzenia do niego podwójnego napięcia odniesienia o wartości zależnej od zakresu napięcia wejściowego. W naszej aplikacji poziom przetwarzanego napięcia zawiera się w zakresie 0 – 5V, dlatego napięcia odniesienia odpowiednio wynoszą: UREF- = 0V, UREF+ = 5V. Wyjścia danych przetwornika zostały dołączone do wspólnej magistrali danych. Uaktywnienie przetwornika odbywa się przy niskim poziomie sygnału CS.

Sygnały uaktywniające obydwa przetworniki dołączone są odpowiednio do końcówek P3.0, P3.1 mikrokontrolera. Układ pracuje w trybie READ – ONLY (końcówka MODE podłączona do masy).

Układ TLC 7226 zawiera w swej strukturze cztery 8 – bitowe przetworniki C/A o wspólnym wejściu cyfrowym. Czas przetwarzania sygnału jest mniejszy niż 5μs. Zakres napięcia wyjściowego przetwornika wynosi w naszej aplikacji 0 – 5V, więc dołączone napięcie odniesienia UREF ma wartość 5V. Konstrukcja przetwornika wymaga zasilania go napięciem wyższym niż napięcie odniesienia UREF (VDD > UREF +4V), więc zastosowaliśmy zasilanie 12V. Na rysunku 3.10 przedstawiony jest widok obudowy układu wraz z opisem końcówek sygnałowych.

Rysunek 3.10. Widok obudowy układu TLC 7226 wraz z opisem końcówek sygnałowych.

Układ ten podobnie jak wcześniejszy podłączony jest do wspólnej magistrali danych. Wejścia adresowe A0,A1 podłączone są do portu P2 mikrokontrolera.

Kontroler obsługuje przetworniki na zasadzie korzystania z zewnętrznej pamięci danych (połączone sygnały WR i RD przetworników oraz mikrokontrolera, zapis i odczyt danych odbywa się za pomocą rozkazów MOVX).

W przestrzeni adresowej przetworniki C/A są umieszczone pod następującymi adresami:

C/A1(U4/1 TLC7226) – 0x0h;

C/A2(U4/2 TLC7226)- 0x100h;

C/A3(U4/3 TLC7226)- 0x200h;

C/A4(U4/4 TLC7226)- 0x300h;

Zapis danych do przetworników odbywa się sygnałem WR (generowanym automatycznie przy wykonywaniu rozkazu MOVX), po uprzednim wpisaniu adresu do rejestru DPTR. Poniżej przedstawiony jest fragment kodu programu ilustrujący sposób adresowania pierwszego przetwornika.

MOV DPL,#0b

MOV DPH,#0b

MOV @DPTR,A

Przetworniki A/C umieszczone są w przestrzeni adresowej pod następującymi adresami:

A/C1(U3 TLC0820)- 0x200h;

A/C2(U2 TLC0820)- 0x300h;

Odczyt odbywa się za pomocą sygnału RD po uprzednim ustawieniu linii CS (dla U3 – P3.5; dla U2 – P3.4). Poniżej przedstawiony jest fragment kodu ilustrujący odczyt danych z przetwornika A/C.

MOV P3,#11011111b

MOV DPL,#0b

MOV DPH,#00000010b

MOVX A,@DPTR

MOV P3,#11111111b

Blok zasilania został zbudowany w oparciu scalone układy stabilizatorów LM 7805 i LM 7812 mających napięcie wyjściowe odpowiednio 5V i 12V. Napięcie wejściowe bloku zasilającego powinno wynosić około 14V.

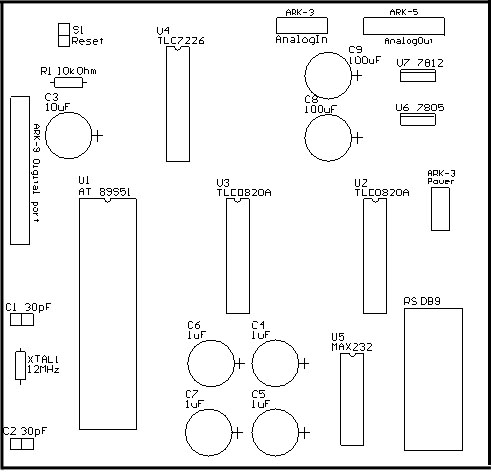

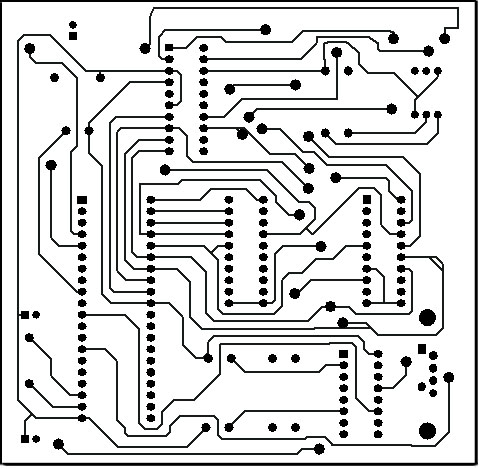

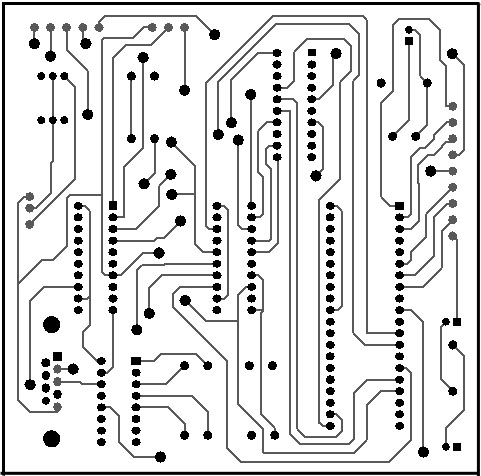

Projekt płytki obwodu drukowanego wykonany został w programie PROTEL. Grubość ścieżek na zaprojektowanej płytce wynosi 0,3 mm z 1 mm odstępem pomiędzy ścieżkami. Płytka została wykonana bez metalizacji otworów, dlatego konieczne było zastosowanie pod układy scalone podstawek precyzyjnych, umożliwiających lutowanie ich z obydwu stron druku. Na poniższych rysunkach przedstawione są widoki górnej i dolnej warstwy mozaiki ścieżek oraz widok rozkładu elementów.

Rysunek 3.11. Widok rozkładu elementów.

Rysunek 3.12. Widok górnej warstwy mozaiki ścieżek.

Rysunek3.13. Widok dolnej mozaiki ściezek.

Oprogramowanie części sprzętowej modelu

Kod źródłowy programu został napisany w języku ASEMBLER dla mikrokontrolerów z rodziny ’51. Kompletny kod źródłowy programu zamieszczony został w dodatku [***] na końcu pracy. Poniżej przedstawiony jest ogólny algorytm działania programu.

Rysunek 3.14. Algorytm głównej części programu

Rysunek 3.15. Algorytm obsługi przerwania od portu szeregowego

Idea działania programu jest następująca:

Po starcie inicjalizowane są wszystkie zmienne oraz ustawiane ich wartości początkowe.

Port szeregowy pracuje w trybie pierwszym. Ramka danych składa się z bitu startu, ośmiu bitów danych oraz bitu stopu. Prędkość transmisji ustalana jest programowo i w naszej aplikacji wynosi 1200 bod. Po odblokowaniu przerwania od portu szeregowego kontroler przechodzi w stan oczekiwania na przerwanie. Przerwanie może być zgłoszone zarówno przez nadajnik jak i odbiornik portu szeregowego. Z chwilą nadejścia przerwania kontroler przechodzi do jego obsługi. Na stosie zapamiętywane są wszystkie wartości rejestrów statusowych PSW i ACC , a odebrana wartość znajdująca się w buforze portu szeregowego jest dekodowana. W zależności od typu odebranego polecenia adresowany jest właściwy przetwornik (analogowo – cyfrowy dla polecenia odczytu lub cyfrowo – analogowy dla polecenia zapisu). Jeśli zaadresowany jest przetwornik A/C to mikrokontroler odczytuje jego stan, a odczytana wartość wysyła na port szeregowy. Gdy zaadresowany jest przetwornik C/A to mikrokontroler oczekuje na odbiór kolejnego bajtu z portu szeregowego, a następnie odebrana wartość zapisywana jest do przetwornika. Po zakończeniu tych operacji przywracane są zawartości rejestrów statusowych, a mikrokontroler przechodzi w stan oczekiwania na kolejne przerwanie.

Komunikacja części sprzętowej modelu ze środowiskiem LabView

Zgodnie z założeniami dotyczącymi części sprzętowej modelu komunikacja odbywa się za pomocą transmisji szeregowej o standardzie RS 232. W celu umożliwienia współpracy obydwu części modelu należało ustalić zasady komunikacji (ramkę polecenia). Poniższa tabela przedstawia schemat zastosowanej ramki poleceń.

Tabela 3.3 Schemat ramki sterującej.

| LSB | MSB | Polecenie | ||||||

| W | R | C | Adres | |||||

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | Zamykanie sesji |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Zapis do C/A 1 |

| 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | Zapis do C/A 2 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | Zapis do C/A 3 |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | Zapis do C/A 4 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | Zapis do portu P1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | Odczyt z portu P1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | Odczyt z A/C 1 |

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | Odczyt z A/C 2 |

Ramka sterująca jest 8 –bitowa . trzy najstarsze bity określają rodzaj wykonywanej operacji (WRITE , READ, CLOSE). Na następnych trzech bitach zakodowany jest adres urządzenia, natomiast dwa najmłodsze bity nie są używane. Trzybitowa przestrzeń adresowa umożliwia zaadresowanie ośmiu urządzeń.

Polecenie zamknięcia sesji CLOSE powoduję wyzerowanie stanu przetworników oraz portu cyfrowego.

Ustalona ramka polecenia umożliwia łatwą implementację jej zarówno w języku ASEMBLER jak i w środowisku LabView.

Aplikacja diagnostyczna w środowisku LabView

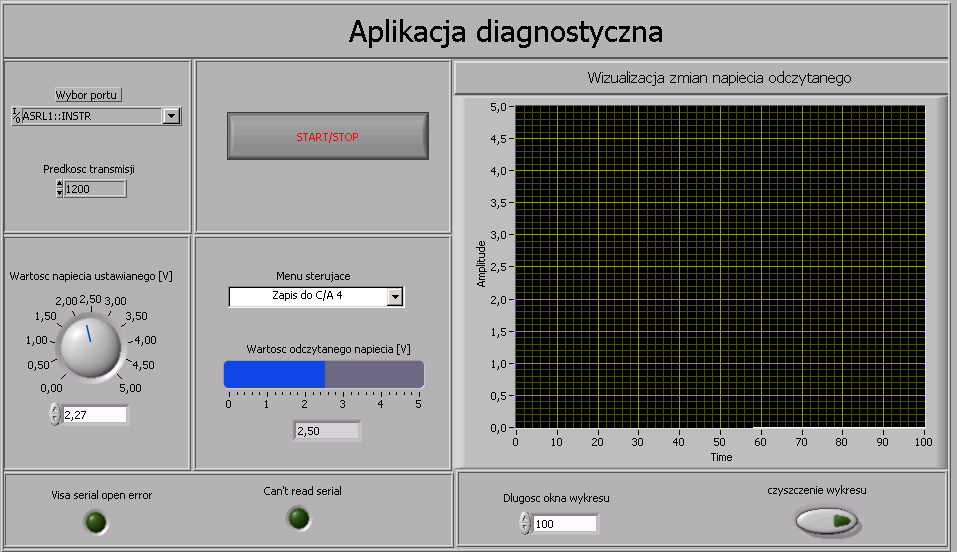

W celu sprawdzenia poprawności pracy części sprzętowej modelu w programie LabView została zbudowana aplikacja kontrolno – sterująca, której schemat oraz widok panelu głównego przedstawiony jest na poniższych rysunkach.

Rysunek 3.16. Widok panelu głównego aplikacji diagnostycznej

Zbudowana aplikacja umożliwia sterowanie przetwornikami A/C i C/A oraz portem cyfrowym.

Przed uruchomieniem aplikacji należy wybrać port do którego podłączone jest urządzenie mikroprocesorowe oraz ustalić prędkość transmisji na 1200 bod. Następnie z menu sterującego należy wybrać rodzaj wykonywanej operacji. Jeśli wybrano zapis, to za pomocą potencjometru należy ustawić wartość napięcia wyjściowego przetwornika C/A. Gdy wybrano odczyt, to na wykresie będzie przedstawiony przebieg napięcia wejściowego wybranego przetwornika A/C. W przypadku gdy z menu sterującego wybierzemy opcje „Zamykanie sesji” , to wszystkie przetworniki oraz port cyfrowy zostaną wyzerowane.

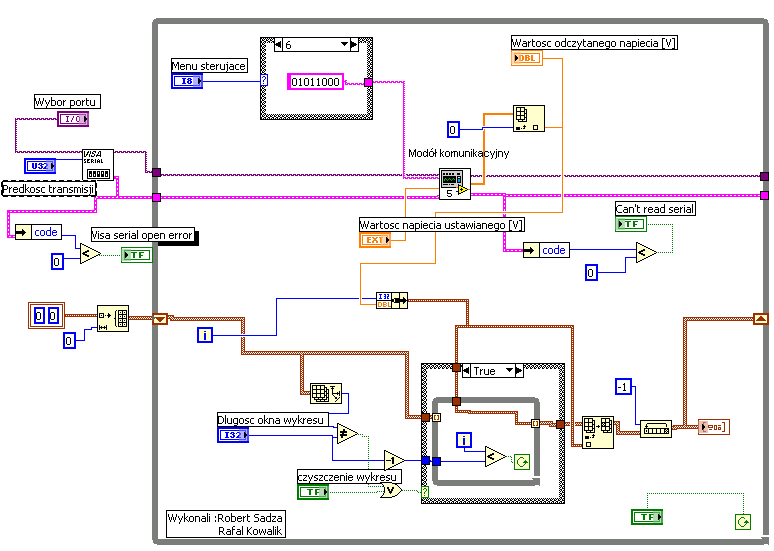

Rysunek 3.17. Schemat aplikacji diagnostycznej

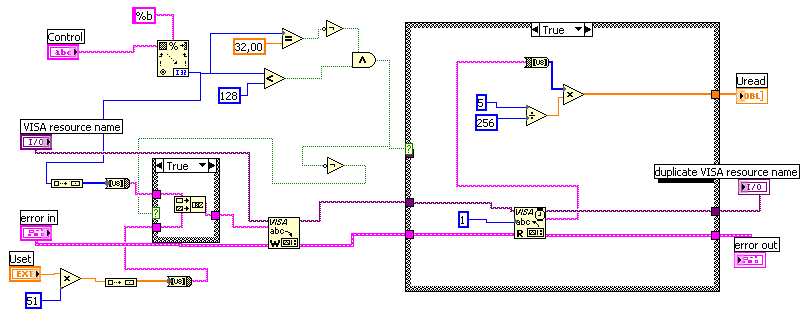

Blok oznaczony jako „moduł komunikacyjny” bezpośrednio odpowiada za współpracę urządzenia mikroprocesorowego z aplikacją LabView. Jego struktura wewnętrzna umożliwia przetworzenie wartości napięć z poziomu panelu głównego na wartości sterujące przetwornikami oraz obsługę portu szeregowego. Na poniższych rysunkach przedstawiona jest struktura wewnętrzna oraz opis wyprowadzeń modułu komunikacyjnego.

Rysunek 3.18. Struktura modułu komunikacyjnego

Rysunek 3.19. Opis wyprowadzeń modułu komunikacyjnego

Znaczenie poszczególnych wyprowadzeń:

„VISA resource name” - nazwa zasobu,

“Control” – rodzaj wykonywanej operacji (wartości zgodne z ramką poleceń),

„Uset” – wartość napięcia przetwornika C/A,

„Error in” – wejściowa informacja o błędzie,

„Duplicate VISA resource name” – nazwa zasobu,

“Uread” – wartość napięcia przetwornika A/C

„Error out” – informacja o błędzie.

komentarze

Copyright © 2008-2010 EPrace oraz autorzy prac.